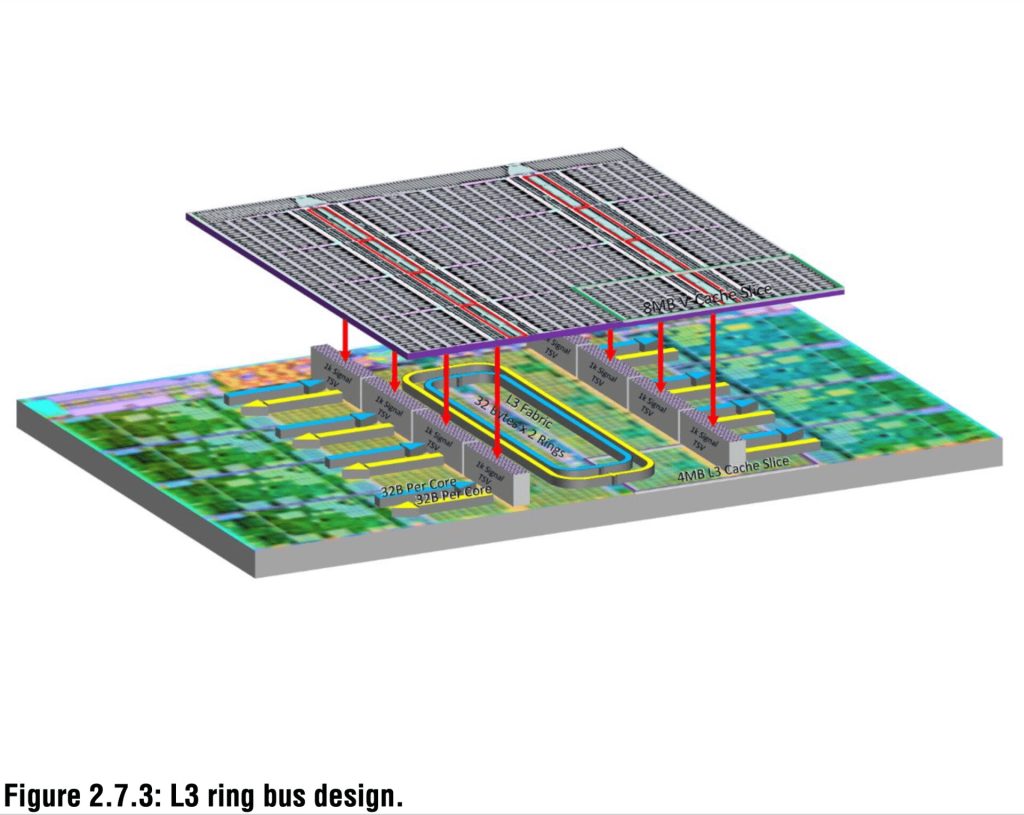

En una de las sesiones realizadas en línea esta semana en la Conferencia Internacional de Circuitos de Estado Sólido, AMD compartió más detalles sobre su diseño 3D V-Cache. La parte interesante aquí es el diseño general de AMD 3D V-Cache y cómo interactúa con la CPU. Se dice que el chip de caché en sí tiene un tamaño de 36mm² y se conecta directamente a la memoria caché L3 a través de una interfaz de silicona o TSV. Para permitir que todos los núcleos de la CPU se comuniquen con 3D V-Cache, AMD implementó un diseño de bus de anillo compartido en el nivel L3. Se dice que todo el caché L3 está disponible para cada núcleo, lo que ayudará aún más al rendimiento.

El 3D V-Cache consta de múltiples “segmentos” de 8MB con una interfaz de 1024 pines a un solo núcleo de CPU, para un total de 8192 conexiones entre CCX y 3D V-Cache. Esto permite más de 2 terabytes por segundo de ancho de banda por segmento en modo dúplex completo. Esto debería permitir la velocidad L3 completa de 3D V-Cache, aunque no sea una parte integrada de CCX. También se dice que AMD mejoró el diseño CCX del próximo Ryzen 7 5800X3D de varias maneras en un intento por reducir el consumo de energía mientras aumenta la velocidad del reloj. AMD no ha revelado una fecha de lanzamiento para Ryzen 7 5800X3D, pero antes de que llegue Zen 4, será interesante ver si 3D V-Cache y varias pequeñas optimizaciones pueden hacerlo competitivo con las CPU Alder Lake de Intel.

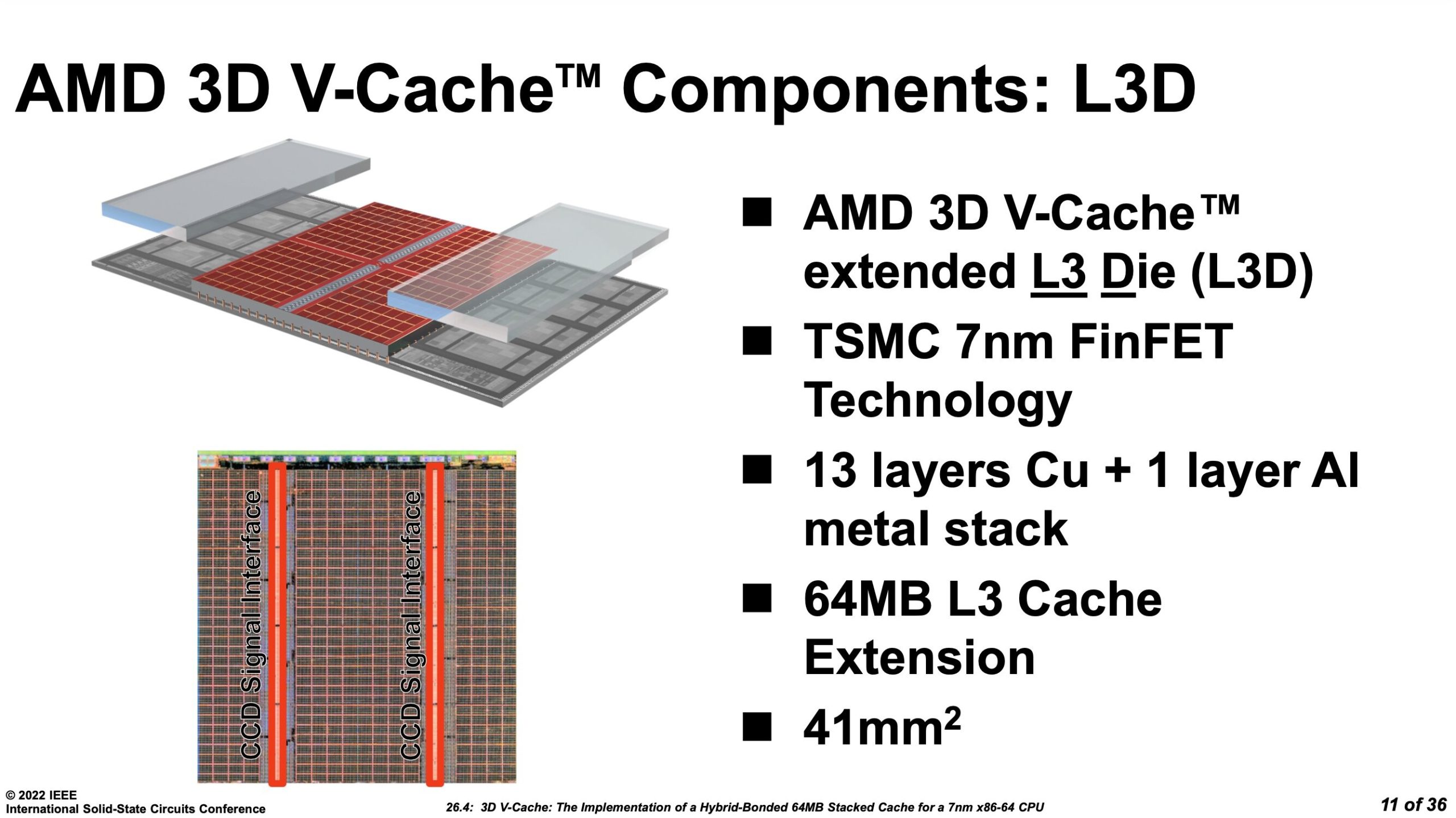

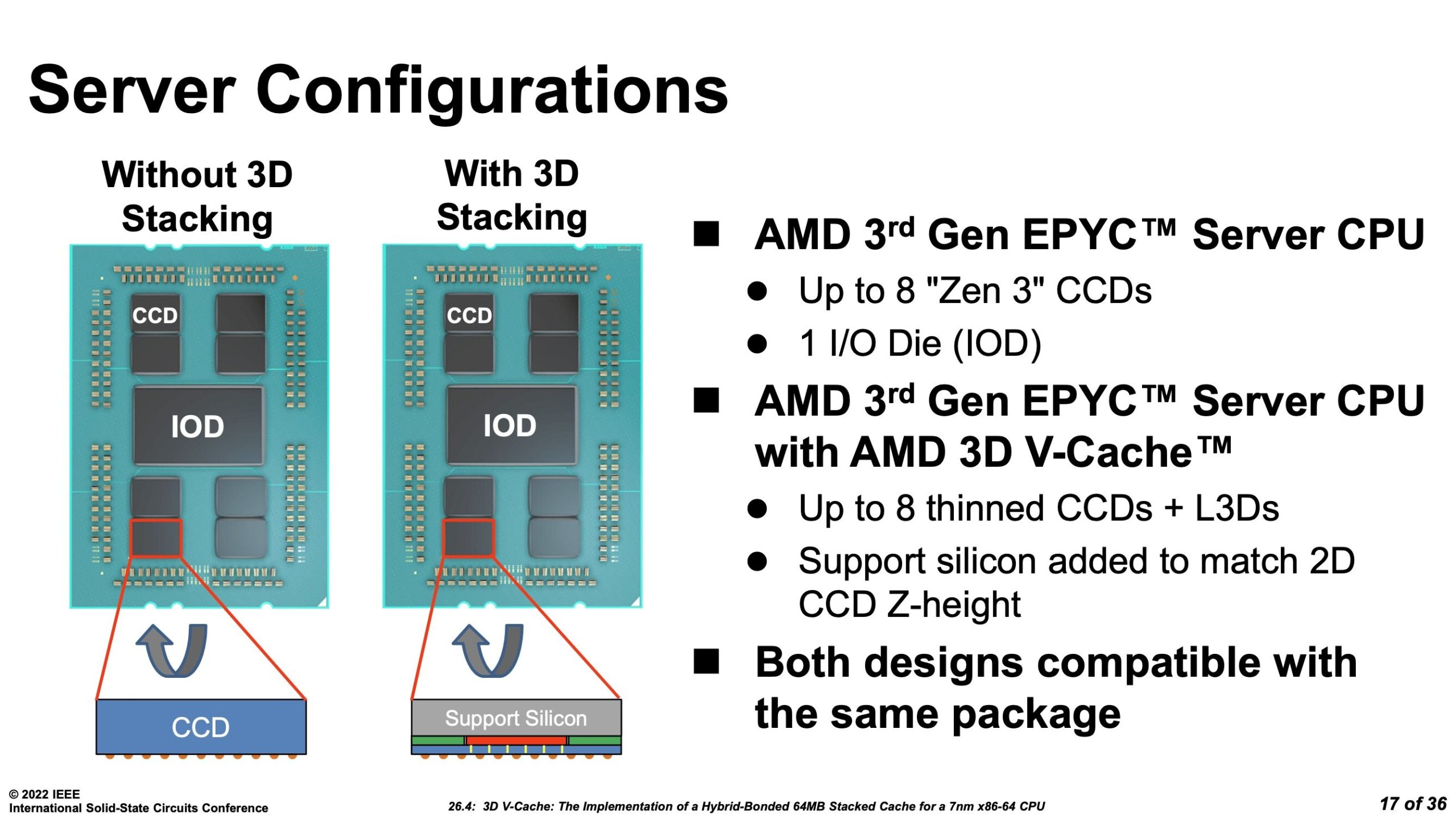

Actualización: se han publicado varias diapositivas de la presentación de AMD, que revelan algunos detalles adicionales. En primer lugar, TSMC fabrica la SRAM para 3D V-Cache en el nodo N7. AMD lo llama un “chip L3 extendido” en la presentación de diapositivas, junto con una expansión de caché L3 de 64MB. La SRAM 3D V-Cache mide 41mm2 y AMD diseñó dos soportes estructurales CCD adicionales para ayudar a disipar el calor. Para encajar todo en el mismo paquete que la CPU de la generación anterior, AMD tuvo que reducir el CCD y el caché L3, y el soporte de estructura también estaba ahí para proteger estas partes reducidas más allá del área cubierta por el 3D V-Cache.